I3C的硬體電路設計

問題:

我看NXP i.mx95的SOC端I3C有三個pin: I3C_SDA, I3C_SCL, I3C_PUR

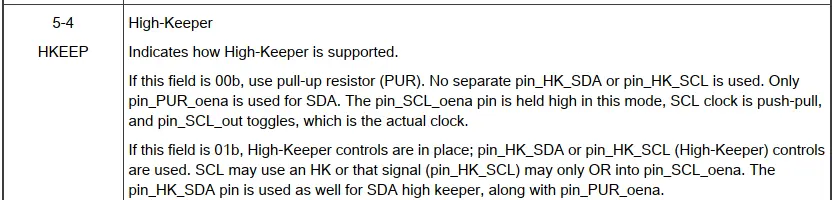

I3C_PUR作用我有些不理解,其在i.mx95 reference manual的描述如下:

Pull up resistance. There is an internal pullup resistance on SDA, which the I3C

controls. If the internal pullup is not enough, PUR can control an external pullup

resistance on SDA actively. See the chip-specific I3C information on whether

this external pullup is available on your chip.其I3C controller中的Controller Configuration (MCONFIG)有一個欄位"HKEEP"設定與PUR有關,描述如下:

If this field is 00b, use pull-up resistor (PUR). No separate pin_HK_SDA or pin_HK_SCL is used. Only

pin_PUR_oena is used for SDA. The pin_SCL_oena pin is held high in this mode, SCL clock is push-pull,

and pin_SCL_out toggles, which is the actual clock.

If this field is 01b, High-Keeper controls are in place; pin_HK_SDA or pin_HK_SCL (High-Keeper) controls

are used. SCL may use an HK or that signal (pin_HK_SCL) may only OR into pin_SCL_oena. The

pin_HK_SDA pin is used as well for SDA high keeper, along with pin_PUR_oena.

Use HKEEP = 10b for I2C modes.

Use HKEEP = 00b or 01b for I3C modes.Your chip may not support any or all High-Keeper methods. You must check the availability

of High-Keeper methods.NOTE

00b - None

01b - WIRED_IN

10b - PASSIVE_SDA (I2C mode, no clock stretches mode). SDA is open drain, and will be

Hi-Z (high-impedance) for Bus Free (IDLE) and hold. The pin pin_HK_SDA is not used in this

option, only a combination of SDA_oena and pin_PUR_oena are used. SCL is push-pull. The pin

pin_HK_SCL is not used in this option, only pin_SCL_oena is used. Since the controller does

not support multi-controller mode, there is no need to have open-drain SCL for I2C. For a single

controller application, the controller’s SCL output can be a push-pull driver design if there are no

devices on the bus which would stretch the clock.

11b - Reserved看來I3C的SDA/SCL的硬體可以設計成push pull(不須外部pullups)或opendrain(需pullups)其與PUR pin的關係為?因為我們的硬體沒有接I3C_PUR pin,所以應該要設計成push pull或是opendrain?

回答

好的,這是一個非常深入且關鍵的問題。您提供的 Reference Manual 內容正是解開謎團的核心。我來幫您梳理一下 I3C_PUR、push-pull 和 open-drain 之間的關係,以及針對您「沒有接 I3C_PUR pin」的情況該如何設計。

1. I3C_PUR Pin 的真正作用:主動式上拉 (Active Pull-up)

首先,要理解 I3C 協議的一個核心目標:在維持與 I2C 向下相容 (使用 Open-Drain) 的同時,大幅提升速度。速度的瓶頸往往在於訊號的上升緣 (rising edge)。

- 傳統 Open-Drain:當裝置釋放 (release) bus 時,訊號電壓是靠被動的 (passive) 上拉電阻

和線路總電容 充電來緩慢上升的。上升時間約略與 成正比。想加快,就要用更小的電阻,但這會增加 bus 在低電位時的功耗。 - I3C 的解決方案:引入主動式上拉 (Active Pull-up)。

I3C_PURpin 就是這個功能的控制器。它不是上拉電阻本身,而是去控制一個外部的、更強的上拉電路 (通常是一個 P-MOSFET)。

工作流程比喻:

想像一下把一顆球從水底放開讓它浮上水面。 - 被動上拉 (Passive):球只靠自身的浮力慢慢往上浮。這就是傳統的 Open-drain。

- 主動上拉 (Active):當控制器偵測到球開始上浮時,立刻從水面上方用一根繩子把它猛力拉上來。

I3C_PUR就是控制這根繩子的信號。

這個設計讓 I3C 可以在需要快速拉高電位時(例如結束一個 bit 的傳輸),短暫地啟用一個非常強的上拉,使訊號上升緣變得非常陡峭,從而支援更高的時脈速度。當訊號穩定拉高後,就關閉這個主動上拉,回到被動上拉狀態,以節省功耗。

2. 與 Push-Pull 和 Open-Drain 的關係

I3C 是一個混合模式的匯流排,它會在不同階段使用不同的電氣特性:

- SDA (數據線):

- Open-Drain:在需要與 I2C 裝置溝通、進行仲裁或進行某些 I3C 特定廣播時使用。此時需要外部上拉電阻。

I3C_PUR可在此模式下介入,加速訊號上升。 - Push-Pull:在確定 bus 控制權後,進行高速資料傳輸時 (SDR 模式),Master 會切換到 Push-Pull 模式。此時 Master 會主動驅動高電位和低電位,不需要上拉電阻。

- Open-Drain:在需要與 I2C 裝置溝通、進行仲裁或進行某些 I3C 特定廣播時使用。此時需要外部上拉電阻。

- SCL (時脈線):

- 在 I3C 模式下,SCL 始終由 Master 以 Push-Pull 模式驅動。這也是手冊中提到

SCL clock is push-pull的原因。這簡化了設計,因為 Master 完全控制時脈,不像 I2C 還要處理 Slave 的 "clock stretching"。 - 例外:當

i2cdetect或與純 I2C 裝置通訊時,控制器會切換到 I2C 模式,此時 SCL 也會表現得像 Open-Drain(儘管手冊提到HKEEP=10b時 SCL 仍是 push-pull,這是針對單 Master 場景的優化)。

- 在 I3C 模式下,SCL 始終由 Master 以 Push-Pull 模式驅動。這也是手冊中提到

結論:I3C_PUR 是 Open-Drain 模式下的效能強化選項,與 Push-Pull 模式無關。

NXP i.mx95 reference manual:

Linux kernel i3c driver中HKEEP的預設值為0 ->代表PUR pin只有針對SDA信號做主動式電阻補償

drivers/i3c/master/svc-i3c-master.c

reg = SVC_I3C_MCONFIG_MASTER_EN |

SVC_I3C_MCONFIG_DISTO(0) |

SVC_I3C_MCONFIG_HKEEP(0) |

SVC_I3C_MCONFIG_ODSTOP(odstop) |

SVC_I3C_MCONFIG_PPBAUD(ppbaud) |

SVC_I3C_MCONFIG_PPLOW(pplow) |

SVC_I3C_MCONFIG_ODBAUD(odbaud) |

SVC_I3C_MCONFIG_ODHPP(odhpp) |

SVC_I3C_MCONFIG_SKEW(0) |

SVC_I3C_MCONFIG_I2CBAUD(i2cbaud);

3. 您的情況:沒有接 I3C_PUR pin,該如何設計?

這是最關鍵的部分。既然您的硬體沒有將 I3C_PUR pin 拉出來使用,這代表您無法使用「主動式上拉」這個硬體加速功能。

因此,您的設計必須是標準的 Open-Drain 設計。

- 您應該怎麼做?

- 必須在 SDA 和 SCL 線路上使用外部的被動上拉電阻。這就是我們之前討論的,您需要在 1.8V 和 3.3V 兩側都加上上拉電阻。

- 您的硬體設計本質上就是一個標準的 Open-Drain/I2C 相容設計。這是完全正確的,因為 I3C 控制器向下相容 I2C,並且可以在沒有主動上拉的情況下工作。

- 對 i.MX95 控制器意味著什麼?

- 即使您在軟體中設定

HKEEP = 00b(I3C 模式),控制器雖然會嘗試去驅動I3C_PUR這個 pin,但因為外部沒有對應的電路,所以不會有任何事情發生。 - Bus 的運作將完全依賴您所安裝的被動上拉電阻。

- 這會影響功能嗎? 不會。您的 I3C Bus 依然可以正常工作。只是在 bus 負載(電容)較大時,您能達到的最高速度可能會受到被動上拉電阻的限制,可能無法達到 I3C 規格的理論上限,但在大多數應用中,這完全足夠了。

- 即使您在軟體中設定

總結

- I3C_PUR 的作用:一個選配的 (optional) 控制信號,用於啟動外部的「主動式上拉」電路,以加速 SDA 線在 Open-Drain 模式下的信號上升速度。

- 您的設計選擇:因為您的硬體沒有連接

I3C_PUR,您唯一且正確的選擇就是採用傳統的 Open-Drain 設計,也就是在 SDA 和 SCL 上都必須使用外部的被動上拉電阻。 - 對您當前問題的影響:您目前

i2cdetect掃不到裝置的問題,與I3C_PURpin 無關。問題根源仍然在於基本的 Open-Drain 電路是否完整 (例如缺少 1.8V 側的上拉電阻) 以及 Device Tree 的 Pin Muxing 設定是否正確。請專注於這兩點進行偵錯。

I3C bus的hardware schematic reference design

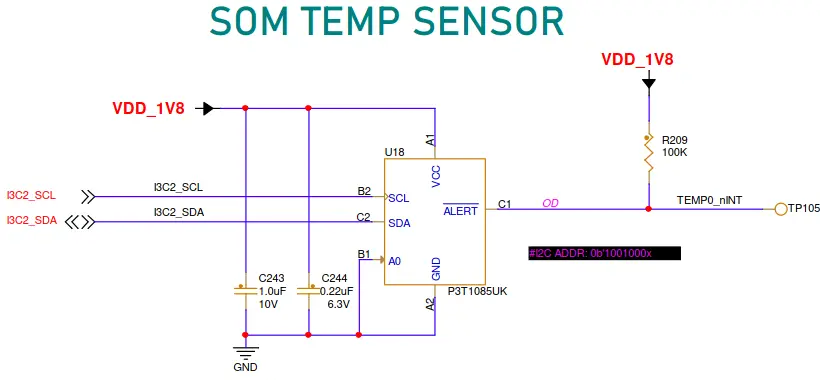

1. i.mx95 EVK 15x15:

D:\Project\137.imx95\evk_schematic\i.MX 95 15x15 IOT EVK\SPF-87751_A.pdf

(SDA/SCL無外部pullups)

但linux 6.12.20 arch/arm64/boot/dts/freescale/imx95-15x15-evk.dts未定義此P3T1085

也許是因為此為optional線路(ethernet MDIO/I3C)二擇一 需跳電阻來將I3C bus連通

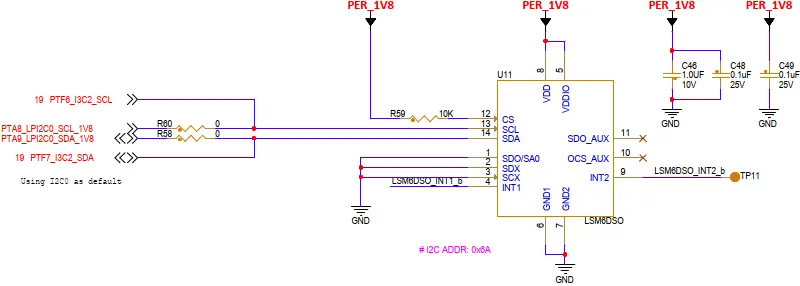

2. i.mx8ulp 9x9:

這是唯一一片NXP的板子有enable I3C

D:\temp\imx8ulp_9x9_schematic\sch-52007_b.pdf

(SDA/SCL無外部pullups)

雖然device tree有定義PUR pin的mux,但實際線路圖上沒接

arch/arm64/boot/dts/freescale/imx8ulp-9x9-evk-i3c.dts

&i3c2 {

pinctrl-names = "default", "sleep";

pinctrl-0 = <&pinctrl_i3c2>;

pinctrl-1 = <&pinctrl_i3c2>;

i2c-scl-hz = <400000>;

status = "okay";

lsm6dso_i3c: imu@6a,208006c0000 {

reg = <0x6a 0x208 0x6c0000>;

assigned-address = <0x6a>;

};

};

&iomuxc1 {

pinctrl_i3c2: i3c2grp {

fsl,pins = <

MX8ULP_PAD_PTE19__I3C2_PUR 0x3

MX8ULP_PAD_PTF6__I3C2_SCL 0x3

MX8ULP_PAD_PTF7__I3C2_SDA 0x3

>;

};

};

3.FRDM-MCXN947

NXP Documentation Portal

沒接外部pullups

結論:

以上三個線路接未通過level shifter,且皆無external pullups.

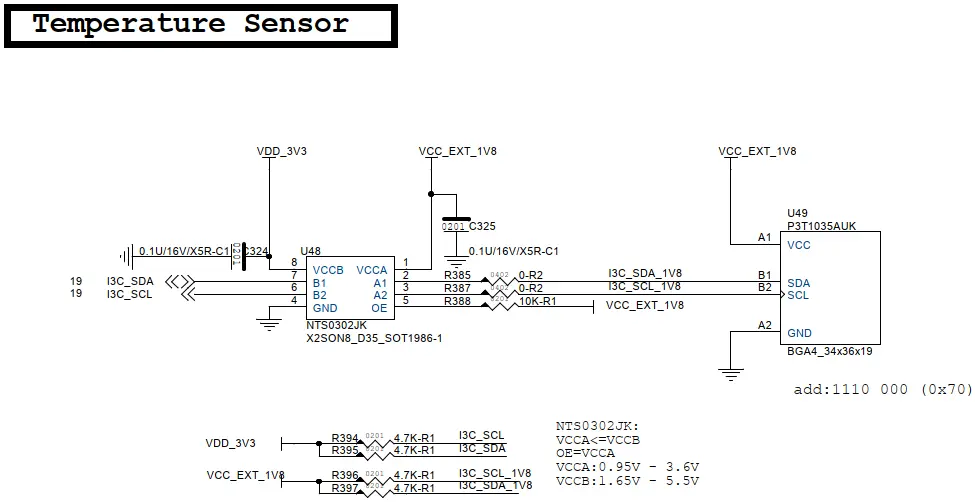

依照

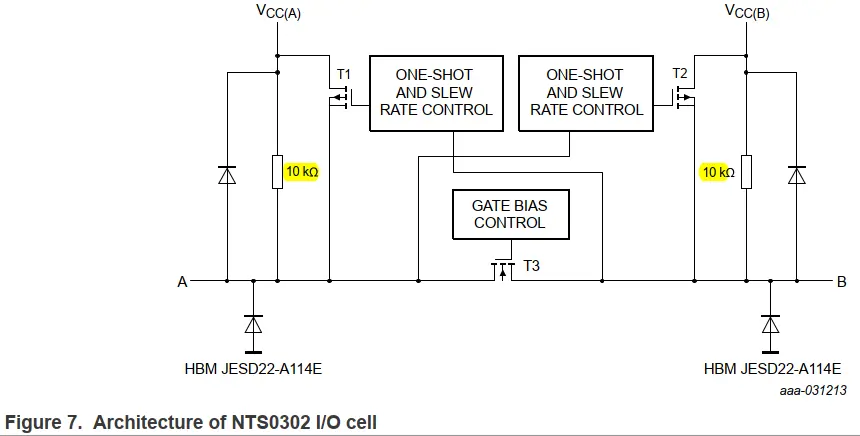

與EDM-IMX95-EVM的線路比較,EDM-IMX95 I3C SDA/SCL的硬體線路有通過level shifter IC "NTS0302"將從SOC出來的SDA/SCL 3.3v轉換成SDA/SCL 1.8V, 而SDA/SCL 3.3v和SDA/SCL 1.8v端各有上拉4.7k ohm電阻

- NTS0302 內建上拉電阻(約 10 kΩ)在 A、B 兩側,其架構圖和敘述寫得很清楚:「Pull‑up resistors are included in the device for DC current sourcing capability」,並在一射(one‑shot)加速期間旁路這些 10 kΩ 以提升上升緣。因此從嚴格需求來說,不一定要外掛上拉電阻。

- 如果你外掛上拉,建議 A(3.3 V)與 B(1.8 V)兩側各自接到各自電壓,讓每一側的「高電位」由該側的電源定義,這是雙電源、雙向 FET 轉換器的常見做法(即使在其他被動 FET 型的 I2C/I3C 轉接器上也是如此)。 [ti.com|ti.com]

- 針對 I3C:標準規範裡 SCL 是 push‑pull、SDA 在某些階段採 open‑drain/在資料傳輸採 push‑pull;一般不需要外部上拉電阻,因為控制器會提供「高保持/動態上拉」能力。加太強的外部上拉只會增加低電位時的耗流,對 SCL 尤其沒有必要。 [tek.com|tek.com], [ti.com.cn|ti.com.cn], [edn.com|edn.com]

上拉電阻的討論

硬體設計可能造成的速度限制

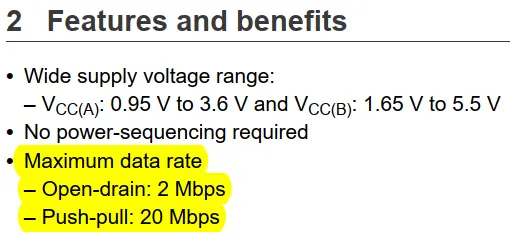

1. NTS0302:

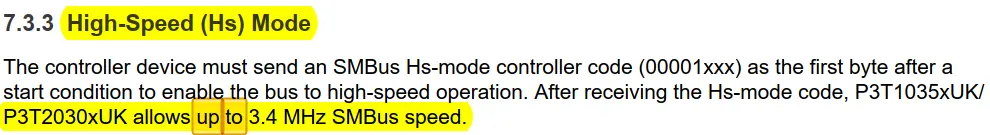

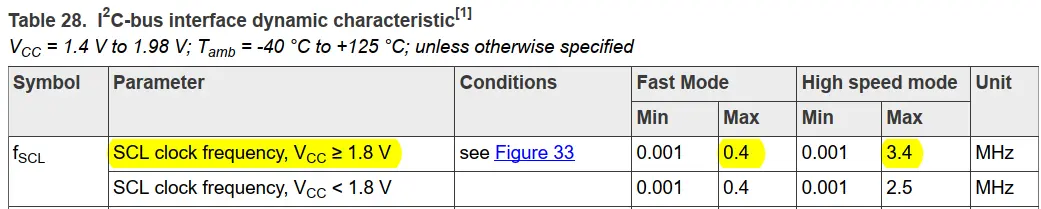

2. P3T1035

I2C模式下:

I3C模式下:(SDR mode)

| P3T1035 (temperature) |

NTS0302 (level shifter) |

||

|---|---|---|---|

| I2C | 400k/3.4M Hz | Open-drain: 2M bps Push-pull: 20 Mbps |

|

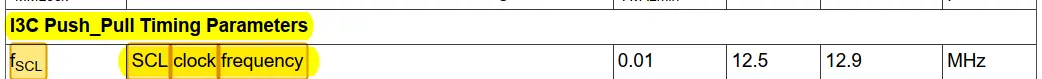

| I3C | 12.9M Hz | Open-drain操作會有問題 | |

| 嘗試: | |||

| I3C |

實務選值與檢核建議

- SCL(I3C):優先不外掛上拉,讓控制器用 push‑pull 驅動。

- SDA:

- 若匯流排純 I3C且控制器有動態上拉/高保持,不必外掛。 [ti.com.cn|ti.com.cn], [edn.com|edn.com]

- 若有 I2C 裝置或較大總線電容,可在 3.3 V 與 1.8 V 兩側各自加上拉(常見 2.2–4.7 kΩ),並評估與 NTS0302 內建 10 kΩ 並聯後的等效值是否符合你的 RC 與耗流預算。 [ti.com|ti.com]

- 檢核 RC 與波形:估算總線電容(含走線、連接器與器件輸入電容),以等效上拉 ReqR_{eq}Req 計算 τ=Req⋅Cτ=R_{eq}\cdot Cτ=Req⋅C,確認在 open‑drain 階段(常 ≤1 MHz)有足夠的上升時間;NTS0302 的 one‑shot 會幫忙邊緣加速,但 DC 的「高」仍由上拉決定。